Have a specialist call me

Leave your details and we will contact you personally.

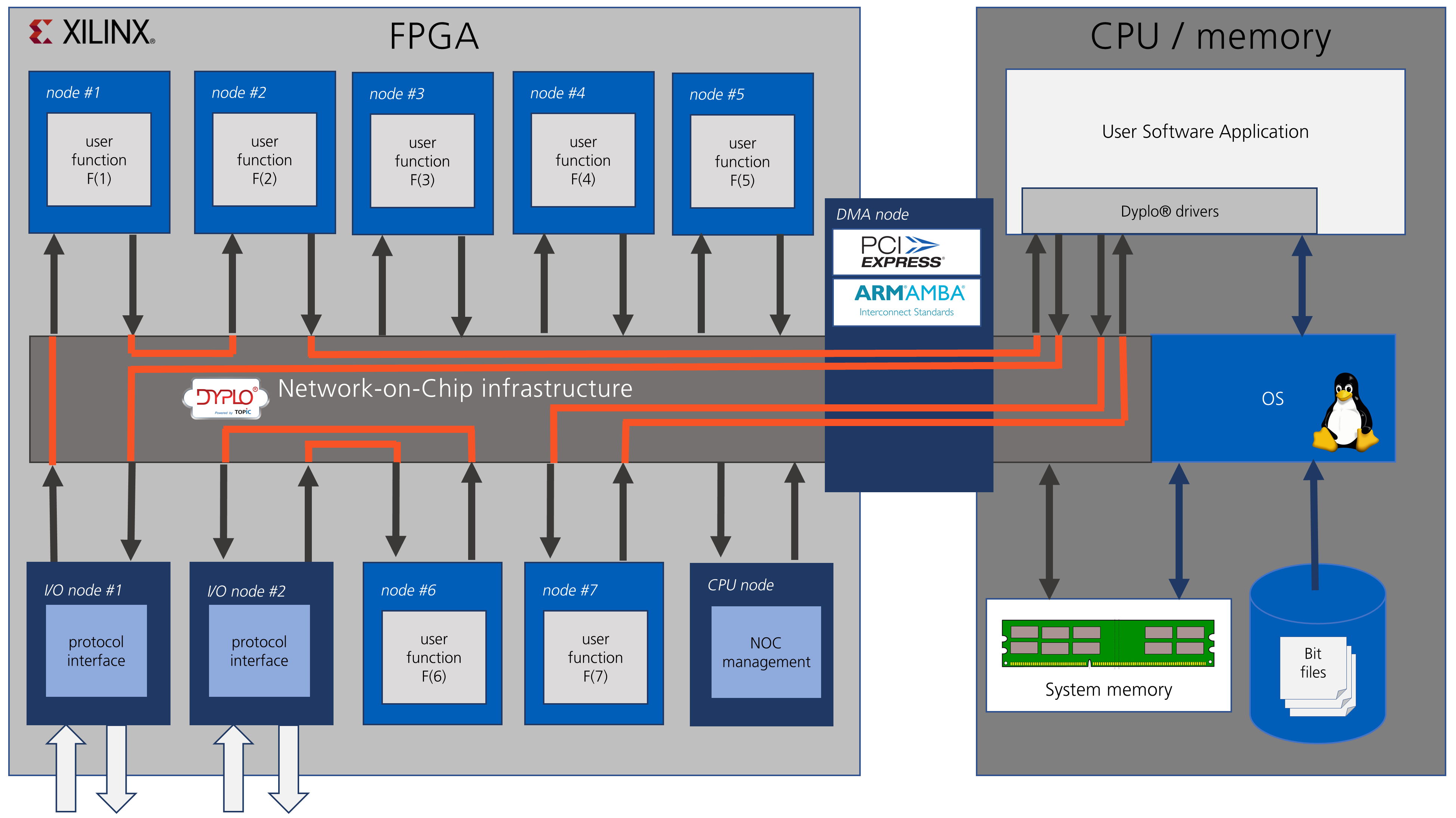

Dyplo stands for Dynamic Process Loader and is an operating system on FPGA fabric. Dyplo provides on demand reconfigurable function blocks on the FPGA, wrapped in a high-performance and effective Network-on-Chip. This allows you to reuse the same FPGA logic for multiple functions over time, resulting in a decrease of FPGA sizes and thus lower power consumption.

Applications can benefit from Dyplo® when FPGA based algorithmic acceleration is required to achieve software performance goals or manage FPGA implemented dynamic processing pipelines. Using Dyplo®, you reduce the complexity of programming FPGA fabric to the level of programming GPU devices using OpenCL coding style. The usage of FPGA fabric for software programmers feels like working with software threads

When integrating functionality of applications running both on the processors as well as the FPGA fabric, require data to be exchanged/shared between the two entities. This is typically where expertise from different disciplines is needed: writing Linux kernel drivers, construction of proper DMA based data exchange mechanisms, high-performance FPGA interfaces according to strict bus protocols and software programming skills. Here multiple programming disciplines meet.

To address this, TOPIC developed Dyplo®, a Dynamic Process Loader. On the FPGA side, Dyplo®forms a Network-on-Chip (NOC), wrapping fixed and dynamically exchangeable FPGA function blocks. On the processor side, Dyplo®is a Linux kernel driver/API that interfaces with the Dyplo®NOC using file baseddata streams. The third aspect of Dyplo®is the implementation flow to transform a software defined function block into a Dyplo®wrapped FPGA function block.

The Dyplo®concept is based on streaming data transport. The FPGA communication infrastructure is loosely inspired by Kahn Processing Networks (KPN). Nodes (accelerator regions) are interacting via a special buffering concept. This synchronizes operations between nodes and matches computational performance with the available communication bandwidth. In the software application, the data from and to the FPGA are available as regular data streams.

Do you have any questions or would you like to know more?

Contact us without obligation.

We are happy to help you personally.

Leave your details and we will contact you personally.

We will contact you by telephone shortly.

Leave your details and we will contact you without obligation.

We will contact you by e-mail shortly.